通信更可取。我很欣赏同时移动所有8个(或16个,或32个…)数据位的简单性和效率,使用一两个控制信号进行握手,而不需要复杂的同步方案。

然而,不久之后,主流的数字通信协议——UART、SPI、I2C等——使用串行接口就变得很明显了,我还注意到,用于专业应用的高级协议有利于串行传输。尽管微控制器和中央处理器(CPU)的内部存储、检索和处理操作需要并行数据,这在某种程度上预示着串行通信需要额外的串行化和反串行化硬件。

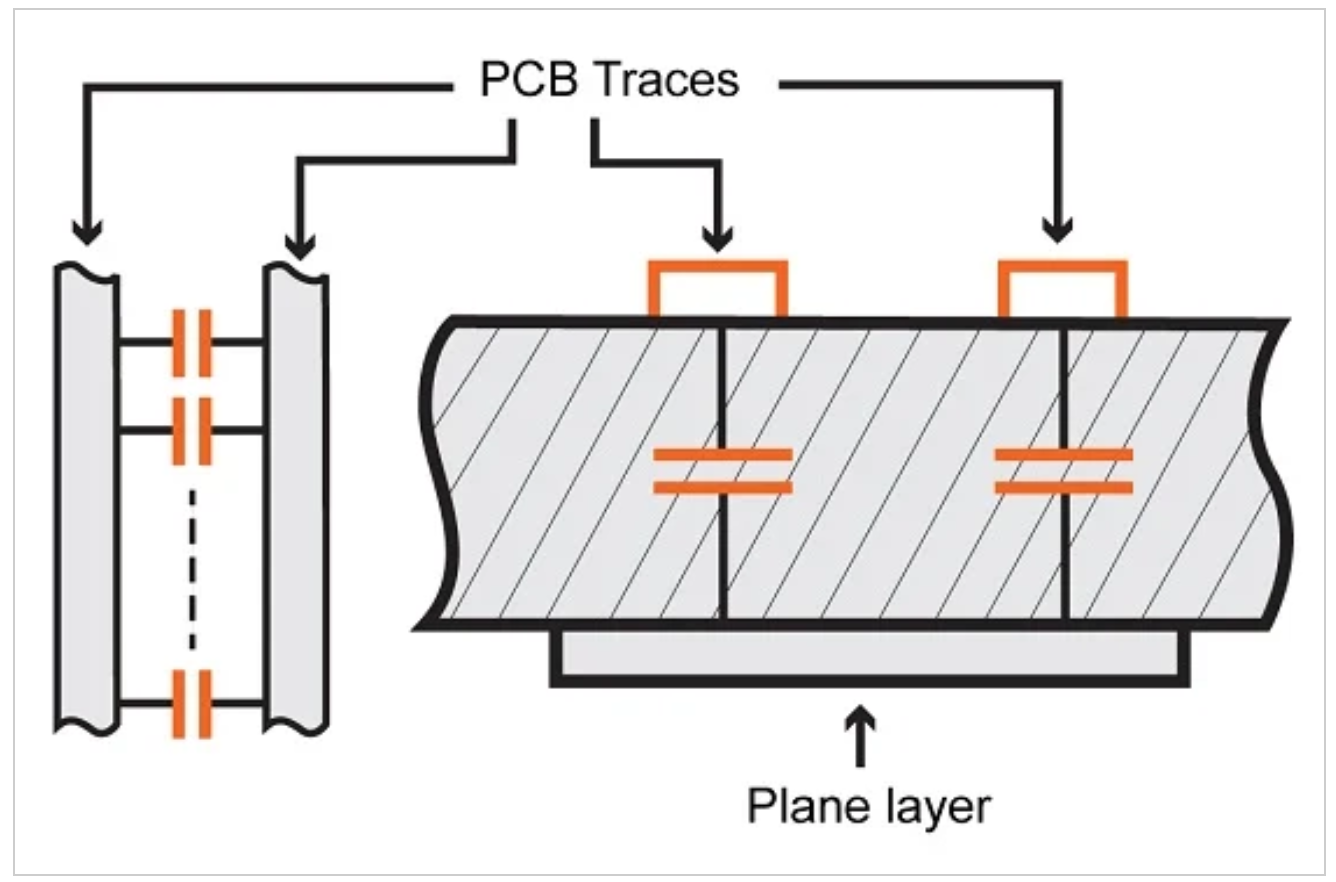

SerDes是一种空间到时间到空间的转换。并行数据同时传输但占用不同的物理互连,串行数据共享相同的物理空间但占用不同时刻(图1)。S

考虑到所有这些,让我们来看看并行数据传输的局限性,然后我将讨论一些突出的SerDes概念。

并联传输的一个更直接的缺点是所涉及的导体数量。如果您仍在8位世界中工作,那么相对于简单、同时的数据传输的好处,使用一组互连似乎是合理的;然而,随着总线位范围,PCB布局任务慢慢的变低效和难以管理。当您不仅必须将数据从一个组件移动到另一个组件,而且必须将数据从不一个PCB移动到另外一个PCB时,问题可能会变得更严重。

此外,这些并行数据线中的每一条都不仅仅是布局和布线人员所关心的问题。紧密间隔的导线所示)容易受到串扰的影响,尤其是在数字信号的高能逻辑转换特性下,更大的导体组更难屏蔽环境电磁干扰(EMI)。

当迹线是原理图中的线时,它们具有完美的电隔离,但在真正的PCB上,它们与附近的迹线和平面层电容耦合。

图2:当迹线是原理图中的线时,它们具有完美的电隔离,但在真正的PCB上,它们与附近的迹线和平面层电容耦合。

对于串行,一些互连就足以传输任何位宽的数据字,并且您能够更好的降低伪逻辑转换的可能性,因为伪逻辑转换会破坏数据或要重新传输,以此来降低通信质量。

理论上,并行确实允许更快的数据传输,但即使是这种优势也比最初看起来更具偶然性。更长的迹线或导线意味着信号将花费更多的时间从发送器传播到接收器,并且随着数据速率的增加,通过匹配迹线长度来均衡整个总线的延迟变得更重要。高速32位总线的跟踪长度匹配并不是一件小事——如果我在进行布局,这将是一个非常有力的支持序列化/反序列化的论点。图3显示了一个弯曲的例子,如果您需要均衡迹线长度,这可能会很有帮助,但当您试图最小化电路板面积时,这就没那么大帮助了。

高速并行总线的另一个问题是功耗过高。串行化能够最终靠将标准逻辑信号转换为低电压差分信号来降低功耗。

SerDes是一个涉及两个独立电路块的过程:在其基本形式中,串行器将由多个同时的数字信号表示的数据(例如由微处理器或ASIC输出)转换为沿一个导体传播的逻辑电平的时间序列。解串器将逻辑电平的这一段时间序列转换回沿着多个导体同时传播的一组信号。

并行到串行的转换不一定将多个导体压缩为一个导体。更普遍地说,序列化的目标是显著减少导体的数量。

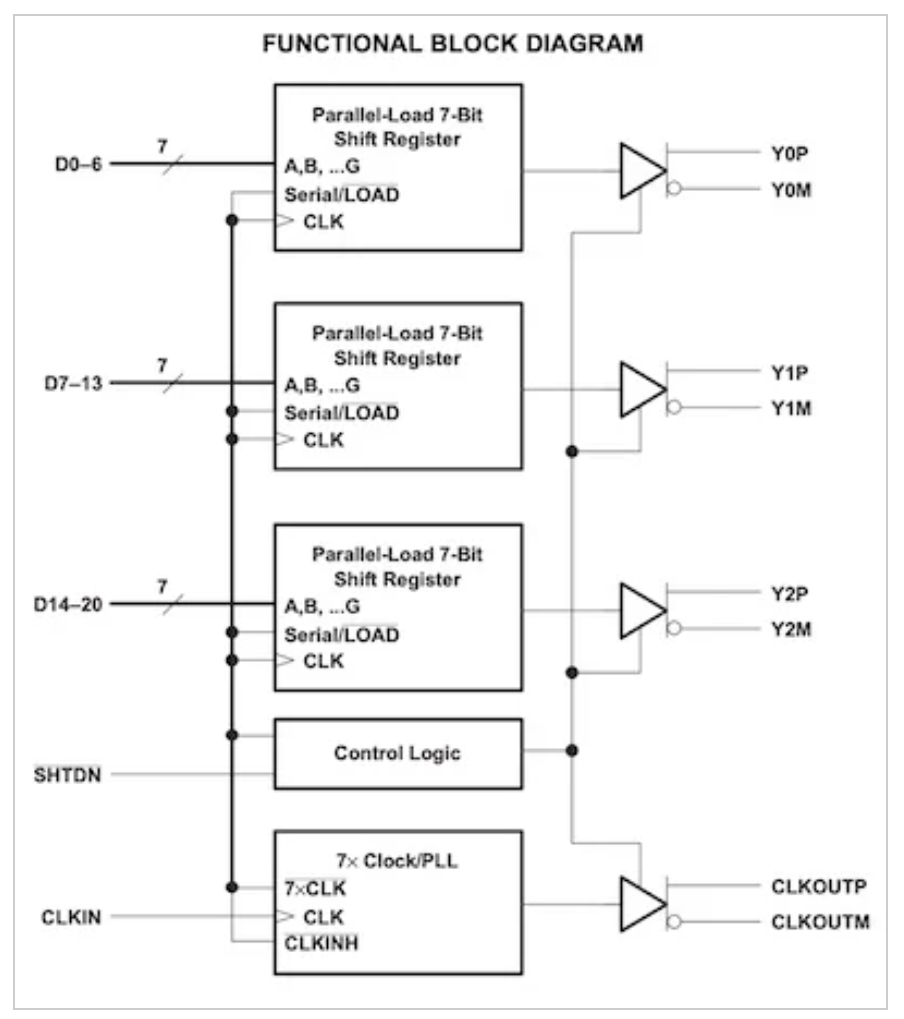

首先,单个串行通信线路常常要两个物理导体,因为许多串行接口,如RS-485和USB,都使用差分信号。此外,吞吐量和接口复杂性之间的最佳平衡可能需要多个串行通道。例如,在下图4的框图中,从TI的SN65LVDS95 LVDS串行器的数据表中,21位并行数据被转换为三个独立的串行输出流。

图4。数据表中SN65LVDS95串行器的功能框图。图片由德州仪器公司提供

如果串行器以特定频率接收并行字,则它必须增加输出比特率,以便将输出字率与输入字率相匹配。由于串行传输比并行传输更适合高位频率,串行化不需要降低吞吐量。如上图所示,锁相环(PLL)可用于根据并行到串行转换中实现的压缩因子来乘以输入时钟。

与任何数字通信接口一样,SerDes需要一些同步机制来确保接收器知道怎么采样和解析传入的逻辑电平。一些系统,包括上图中所示的系统,将时钟信号与数据一起发送。

解串器也可以从输入的串行比特流中获得同步:PLL可以锁定比特流并产生采样时钟。然而,如果输入信号具有不足的转换密度,则PLL将漂移。例如,传感器信号可能在正电源轨处饱和,并被数字化和串行化为逻辑高位的长序列。为避免与低转换密度相关的问题,您可以将SerDes系统与标准(如8b/10b)或自制编码方案相结合

将并行数据传输为串行数据,可以为您提供物理传输选项,否则这是不可行的。即使您的所有信号都位于同一块PCB上,并且所有信号都使用普通迹线进行路由,串行化也可以极大地方便板布局。如果您要将数据从一个板移动到另一个板、从一个模块移动到一个模块或从系统移动到系统,您可能更喜欢使用同轴电缆或光链路。如果你有串行数据,你就可以从普通电线升级到同轴电缆或光纤。

SerDes已成为数字电路不可或缺的一部分。视频接口、电信互连和各种其他应用程序所需的极高数据速率没办法使用并行传输类似地实现。

LM35DZ摄氏温度传感器构成温度量A/D转换为并行三态输出标准微机接口数据总线

由带三线串行接口智能温度传感器DS1620构成的小型电加热器的控温电路

[讨论]ppc860t 的串行调试和scc3,4的中断冲突解决(老站转)

上一篇:联发科出大招:参与设计Armv9新架构 天玑9400旗舰CPU性能能效碾压对手

下一篇:思科 2024 第三财季收入下降 13%,创 2009 年以来最大降幅