反射的出现是因为阻抗失配,端接的出现是为了消除反射。首先我们应该理解反射,为帮助大家理解,我们以水流为例,线路上阻抗不一致,就像水管有粗有细,粗的水管阻力小,细的水管阻力大。既然反射的原因是阻抗粗细不一致,那么要么把细的水管扩宽,要么把粗的水管堵住一部分。

通常在实际电路中,驱动端阻抗比较小,一般13欧姆到30欧姆之间,对应水管是粗的部分,所以驱动端要加串阻。而接收端通常都是高阻,对应到水管是比较细,所以我们应该上下拉电阻。

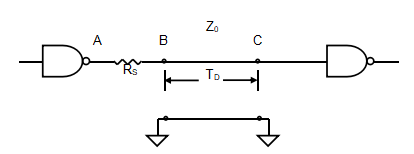

串行端接是通过在尽量靠近源端的位置串行插入一个电阻RS(典型10Ω到35Ω)到传输线中来实现的,如下图所示。串行端接是匹配信号源的阻抗,所插入的串行电阻阻值加上驱动源的输出阻抗应不小于传输线阻抗(轻微过阻尼)。

这种策略通过使源端反射系数为零从而抑制从负载反射回来的信号(抑制二次反射)再从源端反射回负载端。

** 串行端接的优点是:每条线只需要一个端接电阻,无需与电源相连接,消耗功率小。当驱动高容性负载时可提供限流作用,这种限流作用能够在一定程度上帮助减小地弹噪声。而且相对于其它的电阻类型终端匹配技术来说,串联终端匹配技术中匹配电阻的功耗是最小**的,而且串联终端匹配技术不会给驱动器增加任何额外的直流负载,也不会在信号线与地之间引入额外的阻抗,很好的消除了二次反射。

** 串行端接的缺点**在于:对于这种类型的匹配技术,由于信号会在传输线、串联匹配电阻 以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上 的电压实际只有一半的信号电压(概述并不真的就是一半)。

当信号逻辑转换时,由于RS的分压作用,在源端会出现半波幅度的信号,这种半波幅度的信号沿传输线传播至负载端,又从负载端反射回源端,维持的时间为2TD(TD为信号源端到终端的传输延迟),这在某种程度上预示着沿传输线不能加入其它的信号输入端,因为在上述2TD时间内会出现不正确的逻辑态(反射导致的码间干扰)。并且由于在信号通路上加接了元件,增加了RC时间常数从而减缓了负载端信号的上升时间,因而不适合用于高频信号通路(主要由加入的电阻决定)。

另外,采用这种匹配技术时,很难将串联匹配电阻调整到一个非常合适的值. 因为许多驱动器都是非线性的,如TTL 器件,其输出阻抗随着器件逻辑状态的变化而变化,所以串联匹配电阻只能选择一个适中的值. 而且由于许多的驱动器都是非线性的驱动器,驱动器的输出阻抗随着器件逻辑状态的变化而变化, 因此导致串联匹配电阻的合理选择更加复杂。

所以,很难应用某一个简单的设计公式为串联匹配电阻来选择一个最合适的值。且不适合双向传输。

注:对于短的传输线,当最小数字脉冲宽度长于传输线的时间延迟(TD)时,源终端是合乎要求的,因为它消除了驱动器电流部分并联接地的要求。

对于长的传输线,当数字脉冲宽度小于传输线延迟时间(TD)时,负载终端是较好的。因为负载端的反射将反射回源头端,并干扰沿线传播的信号,反射必须在负载端消除。

** 匹配电阻选择原则:** 匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗。常见的CMOS和TTL驱动器,其输出阻抗会随信号的电平大小变化而变化。匹配电阻尽可能靠近驱动端,当双向传输时,靠近信号主动元件附近(如内存条和CPU,靠近CPU)。

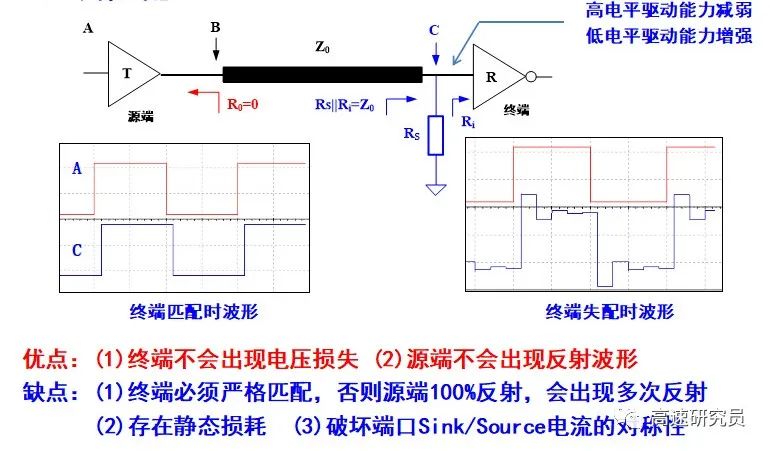

这种端接方式是简单地在负载端加入一下拉到地的电阻RS(RS=Z0)来实现匹配(分流)。采用此端接的条件是驱动端一定要能提供输出高电平时的驱动电流以保证通过端接电阻的高电平电压满足门限电压要求。

在输出为高电平状态时,这种并行端接电路消耗的电流过大,对于50Ω的端接负载,维持TTL高电平消耗电流高达48mA,因此一般器件很难可靠地支持这种端接电路。

优点:并行端接提供了一种简单的设计方法。它是一种最简单的终接方案。在大多数情况下,这种方法只需要一个附加的元件。如果传输线的两端都需要端接就需要两个电阻。

缺点:并行端接浪费了电阻的直流功耗。这种方法无论在高电平还是低电平,都需要驱动端具有稳定的直流,这样就增加了驱动端的直流负载。

当采用并行端接时,一定要注意到,对于TTL级,线欧姆时采用这种端接方案,要求直流输出为24mA((VOH(MIN)=2.4V)。因此,对于电池驱动系统,不推荐采用并行端接方案。

另外,端接电阻要消耗多达0.25瓦的功率(50mA的电流通过100欧姆的电阻),这对于仅消耗几毫瓦的功率的CMOS系统来说是不合适的。

功耗的大小依赖于占空比:对于低占空比,连接电阻到地使得有最低的功耗,对于高占空比,连接电阻到VCC使得有最低的功耗。还有一点就是,大的下拉电阻可能会使下降沿比上升沿快,这会导致占空比内信号的失线)主动并行端接

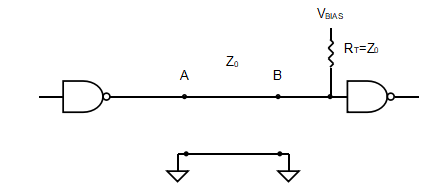

在此端接策略中,端接电阻RT(RT=Z0)将负载端信号拉至一偏移电压VBIAS,如上图所示。VBIAS的选择依据是使输出驱动源能够对高低电平信号有汲取电流能力

。这种端接方式需要一个具有吸、灌电流能力的独立的电压源来满足输出电压的跳变速度的要求。

直流功率损耗,如偏移电压VBIAS为负电压,则输入为逻辑高电平时有直流功率损耗。

、DDR2等SSTL驱动器。采用单电阻形式,并联到VTT(一般为IOVDD的一半)。其中DDR2数据信号的并联匹配电阻是内置在芯片中的。(2)TMDS等高速串行数据

。采用单电阻形式,在接收设施端并联到IOVDD,单端阻抗为50欧姆(差分对间为100欧姆)。匹配电阻选择原则:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等;对双电阻形式来说,每个并联电阻值为传输线特征阻抗的两倍。